### DATA SHEET

# D9050LDDC LPDDR5 Tx Compliance Test Software

Keysight's D9050LDDC LPDDR5 compliance test application software provides a fast and easy way to test, debug and characterize your LPDDR5 designs. LPDDR5 technology offers high data rate of up to 6.4GT/s which enables higher bandwidth for data transfer with lower power. The D9050LDDC offers full test coverage to enable testing of transmitter physical layer of the LPDDR5 DRAM.

## Features

The LPDDR5 compliance test application offers several key features to simplify the validation of your designs.

- Intuitive setup wizard for quick test setup, configuration and test.

- Comprehensive test coverage of the LPDDR5 electrical, timing, eye diagram and jitter tests.

- Offline testing capability with waveform files for completeness of simulation to validation workflow.

- Easy interface to export the test result to the KS6800A series Data Analytics repository for quick analysis with the web-based visualization tool.

# Comprehensive Test Coverage

The LPDDR5 compliance test application allows you to use the oscilloscope to perform automated testing and margin analysis on your LPDDR5 design. The application automatically configures the oscilloscope for each test and provides informative test result. It includes margin analysis indicating how close your device comes to passing or failing each test parameter. The LPDDR5 compliance test automates the measurement as specified in the specification, which helps save test time and design cost.

# **Easy Test Definition**

The test application enhances the usability of Keysight Infiniium oscilloscopes for testing LPDDR5 DRAM. The Keysight automated test framework guides you quickly through the steps required to define the setup, perform the tests and view the test results. You can select a category of tests or select an individual test. The user interface is designed to minimize unnecessary reconnections, which will help save test time and minimize potential operator error. You can save the tests and configurations as project files and recall them for quick testing and review previous results. You can also run the compliance test with saved waveform files from the oscilloscope on your PC, using Offline mode, freeing the oscilloscope for other data acquisition purposes. Offline mode supports waveform files in .wfm or .h5 format.

| 🔟 LPDDR5 Test LPDDR5 project files 0.99.9008                    |                                                      |              |                                                                                |                      |                          |          |  |

|-----------------------------------------------------------------|------------------------------------------------------|--------------|--------------------------------------------------------------------------------|----------------------|--------------------------|----------|--|

| Fil                                                             | File View Tools Help                                 |              |                                                                                |                      |                          |          |  |

| Se                                                              | t Up Select Tests Confi                              | gure Run     | Automate Resu                                                                  | Its HTML Report      |                          | -        |  |

| LPDDR5 Test Environment Setup                                   |                                                      |              |                                                                                |                      | A                        |          |  |

| General Settings                                                |                                                      |              |                                                                                | Signal Source Setti  | ings                     |          |  |

|                                                                 | Test Mode:                                           |              | CK (Diff) (Offline)                                                            |                      |                          |          |  |

| Offline                                                         |                                                      |              | C:\DATA\DDR5_LPDDR5projects\LPDDR5 SI<br>\LPDDR5 waveforms\4184_ 4 to 1\CK.wfm |                      |                          |          |  |

|                                                                 | Data Rate [MT/s]:                                    | WCK Frequen  | cy [MHz]:                                                                      | WCK (Diff) (Offline) |                          |          |  |

|                                                                 | 4184                                                 | 2092         |                                                                                |                      | DDR5projects\LPDDR5 SI   |          |  |

|                                                                 | WCK:CK Ratio :                                       | Clock Freque |                                                                                | UDDDDF               |                          |          |  |

| S                                                               | 4:1                                                  | 523          | DDR5 General S                                                                 | Setup                |                          | ? (= (X) |  |

| ΕT                                                              | Available Signal Source:                             |              | Test Mode —                                                                    |                      |                          |          |  |

| ⊂                                                               | CK (Diff), WCK (Diff), DQ                            |              | 🔵 Live Signal 🔘 Offline                                                        |                      |                          |          |  |

| Р                                                               |                                                      |              |                                                                                |                      |                          |          |  |

|                                                                 |                                                      |              | Data Rate [ MT/s ]                                                             |                      |                          |          |  |

|                                                                 |                                                      |              | JEDEC standard values                                                          |                      |                          |          |  |

|                                                                 |                                                      | ĺ            | 4184                                                                           | JEDEC stand          | uard values              |          |  |

|                                                                 |                                                      |              | WCK : CK Ra                                                                    | tio 4:1 🔽            | WCK Frequency : 2092 MHz |          |  |

| Test Report Comments (Optional) —                               |                                                      |              | Clock Frequency : 523 MHz                                                      |                      |                          |          |  |

|                                                                 |                                                      |              | Signal Source                                                                  |                      |                          |          |  |

|                                                                 |                                                      |              |                                                                                |                      |                          |          |  |

| Messages CK (Diff), WCK (Diff), DQ                              |                                                      |              |                                                                                |                      |                          |          |  |

|                                                                 |                                                      |              | Signal Operation Mode                                                          |                      |                          |          |  |

| 2                                                               | 2019-06-13 02:25:50:444                              | CK (Diff) Co | ontinuous                                                                      |                      |                          |          |  |

| ES                                                              | 2019-06-13 02:25:50:870                              |              |                                                                                |                      |                          |          |  |

| 2019-06-13 02:25:50:884 PM Run end WCK (Diff) Burst WCK options |                                                      |              |                                                                                | tions                |                          |          |  |

|                                                                 | 2019-06-13 02:34:16:020                              | ) PM Continu |                                                                                |                      |                          |          |  |

| E S                                                             | Close 2019-06-13 02:34:19:769 PM Refreshi Show Hints |              |                                                                                |                      | OK Close                 |          |  |

| ŀ                                                               |                                                      |              |                                                                                |                      |                          |          |  |

Figure 1: LPDDR5 application test setup screen. Select the speed grade of your device, Live Signal or Off-line, and signal sources.

# Configurability and Guided Connection

The LPDDR5 compliance test application provides flexibility in your test setup. The application lets you define controls for critical test parameters such as voltage threshold values, number of waveforms used for analysis and customizable violation settings. Once you have configured the tests, the connection page will display the connection diagram for the test you have selected.

You can also specify the number of test trials and only stop running selected tests when the stop condition is met. The application will save the worst-case test result to help you track down the anomalies in your signals.

| LPDDR5 Test LPDDR5 project files 0.99.9008 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                           |                                                                                                                                                                                             |                                                                                                                                  |                       |  |

|--------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------|-----------------------|--|

| File View Tools Help                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                           |                                                                                                                                                                                             |                                                                                                                                  |                       |  |

| Set Up                                     | Select Tests                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | Configure                                                                                                                                                                                                                                                                                       | Run                                                                                                                                                                       | Automate                                                                                                                                                                                    | Results                                                                                                                          | HTML Report           |  |

| SELECT TESTS                               | ✓         LPDDR5 Tr           ✓         Clock A           ✓         Clock           ✓         Clock           ✓         Clock           ✓         Clock           ✓         Clock           ✓         Clock           ✓         tC           ✓         tV           ✓         tV | ransmitter T<br>C Timing Te<br>C Timing Te<br>C (Diff) tests<br>K(avg) Aver<br>K(abs) Abso<br>H(avg) Aver<br>H(abs) Abso<br>CL(abs) Abso<br>t(CC) Maxin<br>CK(abs) Abso<br>VCK(abs) Ab<br>VCK(avg) Av<br>VCK(abs) Ab<br>VCKL(avg) Av<br>VCKL(abs) A<br>VCKL(abs) A<br>CKL(abs) A<br>VCKL(abs) A | ests<br>sts<br>age C<br>olute C<br>rage H<br>age L<br>olute F<br>lute L<br>num C<br>period<br>period<br>period<br>tests<br>rerage<br>verage<br>verage<br>verage<br>verage | lock period<br>igh pulse wid<br>igh pulse wid<br>IIGH Clock p<br>OW Clock pu<br>lock Jitter be<br>d jitter<br>Write Clock<br>e High pulse<br>e Low pulse<br>te HIGH Write<br>/rite Clock Ji | dth<br>Ith<br>Jise widt<br>Ise width<br>etween co<br>period<br>period<br>e width<br>width<br>te Clock p<br>clock pu<br>tter betw | h<br>pnsecutive cycle |  |

| Test:                                      | Test: tjit(CC) Maximum Clock Jitter between consecutive cycles                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                           |                                                                                                                                                                                             |                                                                                                                                  |                       |  |

Figure 2: The Select Tab lists all the tests available in your setup. You can easily setup the individual test or groups of tests.

# **Comprehensive Result Analysis**

In addition to providing you with measurement results, the LPDDR5 compliance test application reports how close your test results are to the specified test limit. You can specify the level at which warnings are to be issued. You are provided a full array of statistics for each measurement.

| Pass                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | #<br>Failed | #<br>Trials | Test Name                                   | Actual Value                | Margin             | Pass Limits                                                            |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|-------------|---------------------------------------------|-----------------------------|--------------------|------------------------------------------------------------------------|

| $\checkmark$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 0           | 1           | Vindiff_CK                                  | 1.745 V                     | 398.6 %            | VALUE >= Vindiff_CK_Limit_Min V                                        |

| $\checkmark$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 0           | 1           | Vindiff CK/2HighPulse                       | 894 mV                      | 410.9 %            | VALUE >= Vindiff_CK_Limit_Min V                                        |

| $\checkmark$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 0           | 1           | Vindiff_CK/2LowPulse                        | 829 mV                      | 373.7 %            | VALUE >= Vindiff_CK_Limit_Min V                                        |

| $\checkmark$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 0           | 1           | VIHdiff_CK                                  | 728 mV                      | 402.1 %            | VALUE >= VIHdiff_CK_Limit_Min V                                        |

| $\checkmark$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 0           | 1           | VILdiff CK                                  | -785 mV                     | 441.4 %            | VALUE <= VILdiff_CK_Limit_Max V                                        |

| <                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 0           | 1           | <u>SRIdiffR_CK</u>                          | 4.814 V/ns                  | 23.5 %             | SR_Limit_Min V/ns <= VALUE <= SR_Limit_Max<br>V/ns                     |

| ✓                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 0           | 1           | <u>SRIdiffF_CK</u>                          | 2.211 V/ns                  | <mark>1.8</mark> % | SR_Limit_Min V/ns <= VALUE <= SR_Limit_Max<br>V/ns                     |

| <ul> <li>Image: A second s</li></ul> | 0           | 1           | tCK(avg) Average Clock period               | 3.639 ns                    | <mark>0.6</mark> % | tCK_avg_Limit_Min s <= VALUE <=<br>tCK_avg_Limit_Max s                 |

| (                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |             | 1           | tCK(abs) Absolute Clock period              | 3.017 ns                    |                    | Information Only                                                       |

| <                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 0           | 1           | tCH(abs) Absolute HIGH Clock pulse<br>width | 517.166290123 mtCK<br>(avg) |                    | tCHL_abs_Limit_Min tCK(avg) <= VALUE <=<br>tCHL_abs_Limit_Max tCK(avg) |

| ✓                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 0           | 1           | tCH(avg) Average High pulse width           | 496.692500000 mtCK<br>(avg) |                    | tCHL_avg_Limit_Min tCK(avg) <= VALUE <=<br>tCHL_avg_Limit_Max tCK(avg) |

| ×                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 1           | 1           | tCL(abs) Absolute LOW Clock pulse width     | 338.559219496 mtCK<br>(avg) | -65.3 %            | tCHL_abs_Limit_Min tCK(avg) <= VALUE <=<br>tCHL_abs_Limit_Max tCK(avg) |

Figure 3: The LPDDR5 test application documents your test parameters, pass or fail status, test limits, measured values and margin.

# **Data Analytics**

The KS6810A data analytics web service software provides an interface that allows the user to export the test result directly to the data repository server via a URL. The user can retrieve the aggregated measurement to be viewed using the visualization tool included in the KS6810A software. The visualization tool provides graphical plots in histogram or line mode that describes the measurement in different test conditions or properties.

# **Thorough Performance Reporting**

The LPDDR5 compliance test application generates HTML reports that captures the performance, status and margins of your device under test. It also captures screenshots of critical measurements of your reference and documentation. This report is suitable for printing and sharing with your test vendors, customers and suppliers.

|                                                                                                                           |                        |                                                                           | t Report<br>I Result: <mark>FAIL</mark> |

|---------------------------------------------------------------------------------------------------------------------------|------------------------|---------------------------------------------------------------------------|-----------------------------------------|

| Test Configuration Details                                                                                                |                        |                                                                           |                                         |

|                                                                                                                           |                        |                                                                           | Application                             |

|                                                                                                                           |                        | Name                                                                      | D9050LDDC LPDDR5 Test                   |

|                                                                                                                           |                        | Version                                                                   | 0.99.9035.0                             |

|                                                                                                                           |                        | Dev                                                                       | ice Description                         |

|                                                                                                                           |                        | Test Mode                                                                 | Live Signal                             |

|                                                                                                                           |                        | Data Rate [MT/s]                                                          | 1500                                    |

|                                                                                                                           |                        | WCK:CK ratio                                                              | 2:1                                     |

|                                                                                                                           |                        | Test                                                                      | Session Details                         |

|                                                                                                                           |                        | Infiniium SW Version                                                      | 64.00.00805                             |

|                                                                                                                           |                        | Infiniium Model Number                                                    | DSO91304A                               |

|                                                                                                                           |                        | Infiniium Serial Number                                                   | No Serial                               |

|                                                                                                                           |                        | Debug Mode Used                                                           | No                                      |

|                                                                                                                           |                        | Compliance Limits                                                         | LPDDR5-800MHz Test Limit (official)     |

|                                                                                                                           |                        | Last Test Date                                                            | 2019-07-17 16:17:02 UTC +08:00          |

| Summary of Results                                                                                                        |                        |                                                                           |                                         |

| Passed     30       Total     32       Margin Thresholds       Warning     < 5 %       Critical     < 0 %                 |                        |                                                                           |                                         |

| Passed     30       Total     32       largin Thresholds       Warning     < 5 %                                          | Actual Value           | Margin Pass Limits                                                        |                                         |

| Passed     30       Total     32       largin Thresholds       Warning     < 5 %                                          | Actual Value<br>522 mV | Margin         Pass Limits           49.1 %         VALUE >= VIndiff      | _CK_Limit_Min V                         |

| Passed 30<br>Total 32<br>argin Thresholds<br>Warning < 5 %<br>Ontical < 0 %<br>ass # Failed # Trials Test Name            |                        |                                                                           |                                         |

| Passed 30<br>Total 32<br>argin Thresholds<br>Warning <5%<br>Critical <0%<br>K Failed # Trials Test Name<br>0 1 Vindiff_CK | 522 mV                 | 49.1 %         VALUE >= Vindiff           48.0 %         VALUE >= Vindiff |                                         |

| Passed     30       Total     32       Hargin Thresholds       Warning     < 5 %                                          | 522 mV<br>259 mV       | 49.1 %         VALUE >= Vindiff           48.0 %         VALUE >= Vindiff | _CK_Limit_Min V<br>_CK_Limit_Min V      |

Figure 4: The LPDDR5 test application generates a summary report for quick results viewing. The report includes details such as test limits, test description and test results.

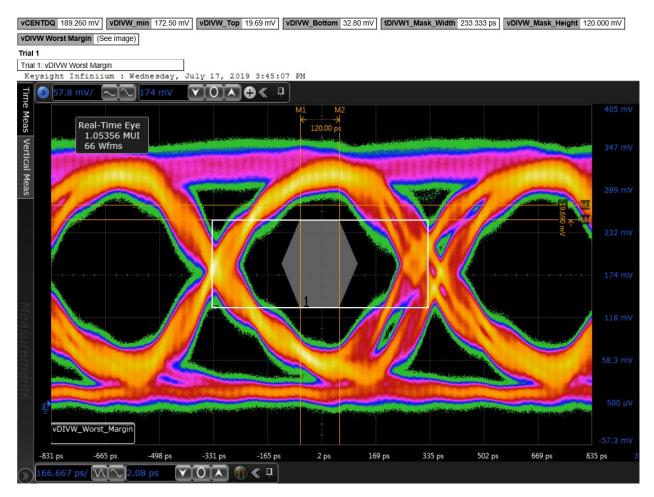

Figure 5: Images of worst-case failures are included in the LPDDR5 summary report for appropriate tests.

# **Recommended Oscilloscope**

The D9050LDDC LPDDR5 software is compatible with the Infiniium series oscilloscopes with operating software revision of 6.40 or higher.

| Data rate         | Minimum bandwidth | Channels   | Description                                        |

|-------------------|-------------------|------------|----------------------------------------------------|

| Up to<br>6.4 GT/s | 16 GHz            | 3 Channels | Infiniium V-Series, Z series,<br>UXR oscilloscopes |

# Ordering Information

### Software

| Model number | Description                                                     | Note     |

|--------------|-----------------------------------------------------------------|----------|

| D9050LDDC    | LPDDR5 Compliance Test Software                                 | Required |

| D9020JITA    | Jitter, Vertical and Phase Noise Analysis Software              | Required |

| D9020ASIA    | Advanced Signal Integrity Software (EQ,<br>InfiniiSim Advanced) | Optional |

| KS6810A      | Data Analytics software (1 license)                             | Optional |

| D9010LSPO    | Infiniium Offline Analysis Software                             | Optional |

## Example of Hardware Configuration

| Model number | Description                          | Quantity                                     |

|--------------|--------------------------------------|----------------------------------------------|

| UXR0164A     | 16 GHz Infiniium oscilloscope        | 1                                            |

| 1169B        | 12GHz InfiniiMax II probe amplifiers | 3                                            |

| N5442A       | Precision BNC adapter                | 3                                            |

| MX0100A      | Micro probe head                     | 1 (includes 5 probe heads, 1 bullet adapter) |

| MX0103A      | Bullet adapter                       | 2                                            |

### Flexible Software Licensing and KeysightCare Software Support Subscriptions

Keysight offers a variety of flexible licensing options to fit your needs and budget. Choose your license term, license type, and KeysightCare software support subscription.

### License Terms

Perpetual – Perpetual licenses can be used indefinitely.

**Time-based** – Time-based licenses can be used through the term of the license only (6, 12, 24, or 36 months).

### License Types

Node-locked - License can be used on one specified instrument/computer.

**Transportable** – License can be used on one instrument/computer at a time but may be transferred to another using Keysight Software Manager (internet connection required).

USB Portable - License can be used on one instrument/computer at a time but may be transferred to another using a certified USB dongle (available for additional purchase with Keysight part number E8900-D10).

Floating (single site) - Networked instruments/computers can access a license from a server one at a time. Multiple licenses can be purchased for concurrent usage.

### KeysightCare Software Support Subscriptions

Perpetual licenses are sold with a 12 (default), 24, 36, or 60-month software support subscription. Support subscriptions can be renewed for a fee after that.

Time-based licenses include a software support subscription through the term of the license.

### Selecting your license:

- Step 1. Choose your software product (eg. D9050LDDC).

- Step 2. Choose your license term: perpetual or time-based.

- Step 3. Choose your license type: node-locked, transportable, USB portable, or floating

- Step 4. Depending on the license term, choose your support subscription duration.

# Learn more at: www.keysight.com

For more information on Keysight Technologies' products, applications or services, please contact your local Keysight office. The complete list is available at: www.keysight.com/find/contactus

KeysightCare Software Support Subscription provides peace of mind amid evolving technologies.

- Ensure your software is always current with the latest enhancements and measurement standards.

- Gain additional insight into your problems with live access to our team of technical experts.

- Stay on schedule with fast turnaround times and priority escalations when you need support.